First, let's briefly understand the concepts of input impedance and electrostatic discharge (ESD).

Input Impedance:

This refers to the rate of change of drain current with respect to gate-source voltage variation between the gate and the source of the MOS transistor. MOS transistors typically have a high input impedance and high insulation performance, meaning that only a very small leakage current passes through the gate. However, this high impedance can reduce the power consumption of the control circuit, allowing it to be used as an input stage for signal amplifiers and switches.

Electrostatic Discharge (ESD):

ESD occurs when the voltage exceeds the insulation capability of the MOS, leading to a sudden increase in current.

There are generally two types of ESD:

Voltage-type: The thin oxide layer of the gate breaks down, forming pinholes that short-circuit between the gate and the source, or between the gate and the drain.

Power-type: The aluminum metallization thin film is fused, causing an open circuit between the gate or the source.

So, back to the original question, why does the MOS transistor's high input impedance fail when exposed to static electricity?

The high input impedance of the MOS transistor means it is very sensitive to input signal currents.

As we know, the MOS transistor is an ESD-sensitive device. Due to its high input impedance and the very small gate-source capacitance, it is highly susceptible to being charged by external electromagnetic fields or static electricity. When static electricity or an external electromagnetic field acts on the MOS transistor, charges are generated on the gate-source capacitance, causing the voltage across the gate-source capacitance to rise.

Due to the high input impedance, these charges cannot be effectively leaked through the input terminal, so the voltage accumulates on the gate-source capacitance, which may cause ESD and even damage the MOS transistor.

As mentioned earlier, the working environment of the MOS transistor is crucial. In an environment with strong static electricity, there are more ions and charges in the air, increasing the accumulation and discharge possibilities of static electricity, further increasing the risk of MOS transistor damage from ESD.

To protect the MOS transistor from ESD damage, the following measures can be taken:

Grounding the gate of the MOS transistor: Connect the gate to a fixed potential to avoid it being floating.

Parallel resistor: Connect a resistor in parallel between Vgs to act as a discharge resistor, releasing the charge.

Place a zener diode: Place a zener diode between Vgs to reduce the risk of external static electricity or high-voltage damage.

In addition, the performance of the device itself is also crucial. Static discharge generates a short-duration high current, with a pulse time constant much smaller than the device's thermal time constant. Therefore, when such a current passes through a small area pn junction or Schottky junction, it instantaneously generates high power density, causing local overheating, and may even cause the local junction temperature to rise above the original temperature of the material, leading to local melting of the junction area, causing pn junction short-circuit, and subsequent complete device failure.

Whether this failure occurs depends mainly on the power density in the internal region of the device. The smaller the power density, the less likely the device is to be damaged. Therefore, selecting high-quality MOS transistors with low power density and good anti-static effects is more conducive to preventing breakdown risks.

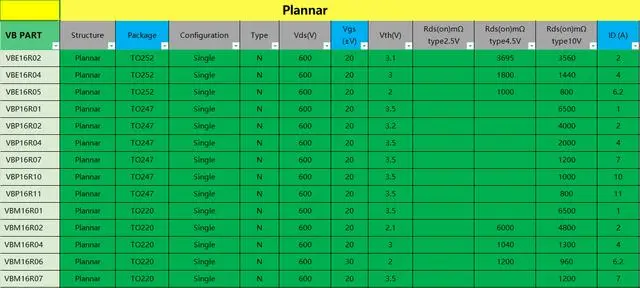

Here, we recommend VBsemi's MOS transistors, which can better prevent static electricity breakdown problems during device application, effectively reducing the risk of device damage.

Advantages of VBsemi's MOS transistors:

Low power consumption: Low static power consumption, suitable for circuits that need to run for a long time.

High speed: Very fast switching speed, can meet the requirements of high-speed circuits.

Strong controllability: The drain current of the MOS transistor can be controlled by adjusting the gate voltage, providing good controllability.

High stability: The gate oxide layer of the MOS transistor has good electrical properties, with high stability and reliability.

* 如果您需要申请我司样品,请填写表格提交,我们会24小时内回复您