Everyone is familiar with Super Junction MOS (SJ MOS), but do you know about the two processes of SJ MOS - Multi-EPI and Deep-Trench? Today, we will analyze the differences between Multi-EPI and Deep-Trench processes of SJ MOS in a simple and clear way.

Multi-EPI and Deep-Trench are two processes of SJ MOS.

Multi-EPI: This process was developed earlier and is more mature. It is based on planar silicon growth technology and uses multi-layer epitaxial growth technology. By doping, thermal diffusion, and growing multiple layers of differently doped epitaxial layers on a silicon substrate, multiple PN junctions are formed, thereby realizing the structure of SJ MOS.

It has higher voltage withstand capability and lower on-resistance. Compared to traditional Super Junction technology, Multi-EPI's SJ technology can achieve higher voltage withstand capability and lower on-resistance, while also reducing production costs. VBsemi has recently launched SJ MOS products based on this advanced technology. Its Multi-EPI Super Junction products have been widely used in power supplies, lighting, electric vehicles, and other fields.

Advantages of Multi-EPI Process:

Since the entire epitaxial process is based on smooth interface growth, there are relatively few epitaxial dislocation defects, which gives it good advantages in terms of leakage, high-temperature reliability, and long-term reliability. The dynamic characteristics of the product are also excellent.

Disadvantages: This preparation process is relatively complex, costly, and the lithography control is relatively difficult.

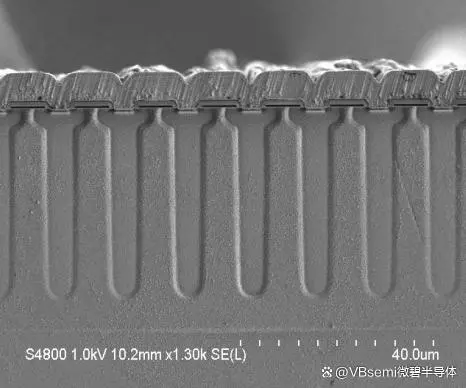

Deep-Trench: This process is a clever way to implement super-junction technology using a relatively simple process. It starts by growing a layer of epitaxial material several tens of microns thick using an epitaxial device. Then, deep and high aspect ratio trenches are etched using a deep etching device. The trenches are then filled by epitaxial growth to form a pillar structure equivalent to the Multi-EPI's pillar structure.

Advantages: Since only one lithography and filling are required, the process is simple and cost-effective. It can reduce crystal defects, thereby improving the reliability and stability of the product.

Disadvantages:

It is difficult to control the etching morphology of the side and bottom of the silicon during deep trench processing.

The process has a large aspect ratio, and during the epitaxial filling process, it is easy to form irregular voids at the bottom of the trench, which may not even be visible under a microscope, leading to a decrease in chip reliability during long-term high-temperature operation.

Due to the interface being close to a abrupt junction, the dynamic characteristics are relatively poorer and can be more tricky to handle in applications.

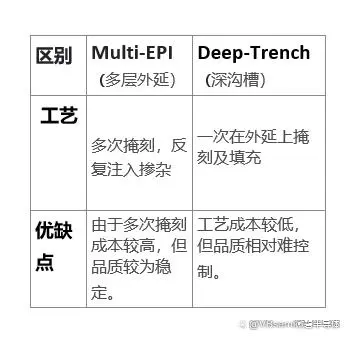

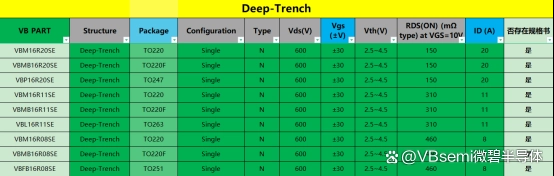

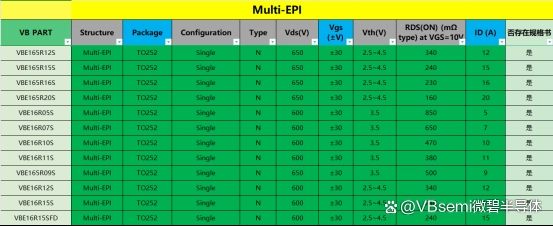

From the above explanations, we can see some differences between the two processes, but both are SJ MOS processes, and both have the advantages of super-junction technology. To help you better understand and choose the type of SJ MOS process, VBsemi has compiled a table for your reference:

Difference between the Two

In addition, compared to traditional MOS products, SJ MOS has many advantages:

Lower RDS(ON) and Vth, leading to lower on-resistance and better on-state characteristics compared to traditional MOS, resulting in lower power consumption and higher efficiency.

Lower leakage current, resulting in lower power consumption and higher efficiency.

However, SJ MOS also has certain disadvantages, especially in terms of surge current capability. Therefore, when using SJ MOS, special attention should be paid to its surge current capability, especially for outdoor products, which need to have a well-designed surge protection circuit.

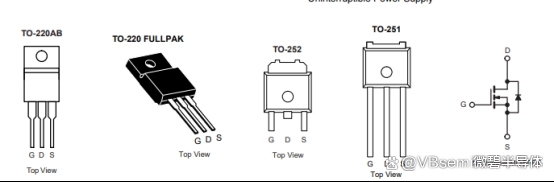

VBsemi has recently launched SJ MOS products based on these two processes, which are suitable for a variety of applications. Both processes have the advantages of increasing current density and breakdown voltage of devices, as well as excellent device performance. The advantages and application analysis of VBsemi's SJ MOS products are as follows:

Low on-resistance: SJ MOS has low on-resistance, which can reduce power loss and improve efficiency.

Lower output capacitance: Due to changes in chip structure, the output capacitance of SJ MOS is much lower than that of traditional MOS, which can improve MOS switch loss.

Smaller gate charge: In power supply design, the gate charge of traditional MOS is relatively large, requiring higher driving ability of the IC. If the IC driving ability is insufficient, it may cause temperature rise and other issues.

Reduced package size: Under the same voltage and current requirements, the chip area of SJ MOS is smaller, which has more space advantages.

SJ MOS is mainly used in power management, motor drive, lighting, communication, and other fields.

* 如果您需要申请我司样品,请填写表格提交,我们会24小时内回复您