Parasitic capacitance and parasitic inductance refer to unintended capacitance and inductance elements existing in a circuit. They are usually caused by factors such as circuit layout, line length, and physical distance between devices.

Parasitic capacitance refers to unintended capacitance elements in a circuit, which can cause problems such as signal crosstalk and poor filtering effects.

Parasitic inductance refers to unintended inductance elements, which can cause problems such as signal attenuation and frequency response distortion. In the circuit design process, it is necessary to consider the impact of these parasitic elements on circuit performance and take corresponding measures for compensation or suppression.

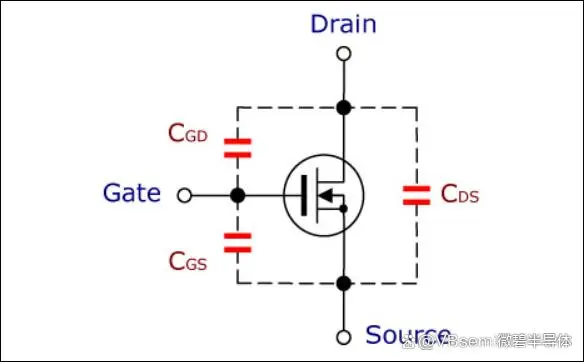

Parasitic capacitance and parasitic inductance can affect the performance and operation characteristics of MOSFETs.

Parasitic inductance is mainly caused by the encapsulation of metal wires and transmission lines, which can cause signal delay and loss. When a signal passes through a MOSFET, parasitic inductance can cause signal delay, reduce switching speed, and may cause signal waveform distortion. In addition, parasitic inductance can also cause energy dissipation of the signal, so it is necessary to consider appropriate compensation methods in the design to reduce its impact.

Parasitic capacitance is mainly caused by the characteristics of the MOS structure, including gate-source capacitance, gate-drain capacitance, and drain-source capacitance. These parasitic capacitances can cause charge accumulation and storage, thereby affecting the switching speed and frequency response of the MOSFET. In particular, gate-source capacitance can cause the hysteresis effect, where the MOSFET still needs some time to fully open or close even after the control voltage reaches the threshold.

To reduce the impact of parasitic inductance and parasitic capacitance on MOSFETs, the following measures can be taken:

Optimize layout and wiring to reduce wire length and area, thereby reducing parasitic inductance.

Use appropriate packaging and ground design to reduce parasitic inductance.

Use insulating materials with low dielectric constant to reduce gate-source capacitance.

Optimize MOS structure design to reduce gate-source and drain-source capacitance.

In conclusion, the impact of parasitic inductance and parasitic capacitance on MOSFETs is an important factor that needs to be considered and addressed. Reasonable design and optimization can reduce their negative effects and improve the performance of MOSFETs.

Note: The information provided in this article is for reference only. Readers should carefully evaluate and follow relevant technical specifications and guidelines in actual applications. Thank you for your attention and support!

* 如果您需要申请我司样品,请填写表格提交,我们会24小时内回复您