Question One: If the gate-source capacitance (Cgs) of a MOSFET is charged and there is no resistor for discharge, will the MOSFET remain on?

Generally, when designing the driver circuit for a MOSFET, the gate of the MOSFET has a parasitic capacitance (Cgs). Typically, when designing the circuit, this Cgs is discharged after the gate is turned off. So, if I don't design a discharge resistor, will the gate-source voltage remain at the turn-on voltage? Will the MOSFET stay on for a long time?

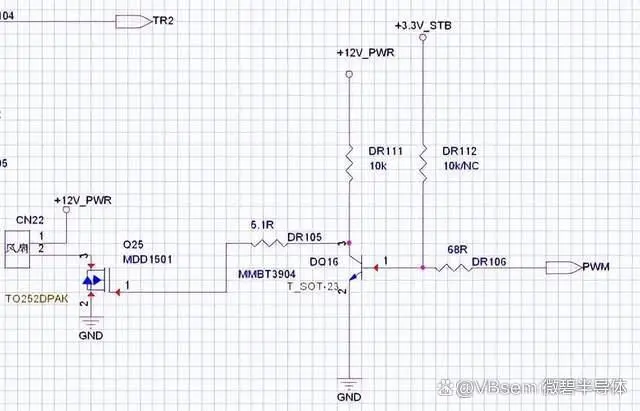

Question Two: I use an NPN transistor to drive an NMOS with a PWM square wave input, as shown in the diagram. How does the gate of the MOSFET become a spike?

I use an NPN transistor to drive an NMOS with a PWM square wave input, as shown in the diagram. How does the gate of the MOSFET become a spike?

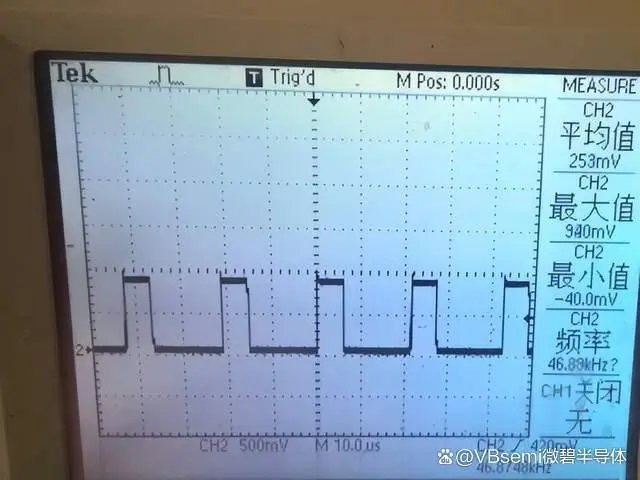

Input PWM signal

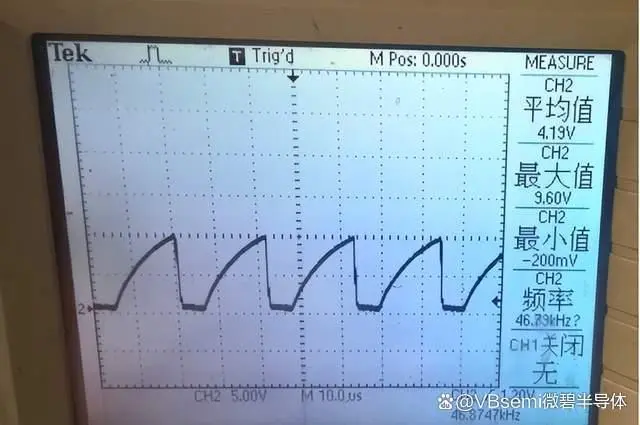

Gate of the MOSFET

Could you please take a look? Could it be caused by the parasitic capacitance of the MOSFET? How can I modify the circuit to improve it?

Note: I have a 220uF capacitor paralleled at both ends of the fan, which is not shown in the schematic. The inductance of the fan to the drain of the MOSFET has been almost DC, and I am puzzled about how the gate of the MOSFET becomes a spike. Theoretically, it should be a square wave, but the current phenomenon is that the high voltage does not immediately rise up as if there is a charging process. How can I eliminate it?

Previous Answers:

Previous Answer One: There is an impedance from the gate of the MOSFET to the ground, generally in the range of MΩ or higher, so the discharge will be very slow. It is recommended to connect a resistor of around 10K.

Previous Answer Two: For the DR111, 10K is too large. Changing to 1K will greatly improve the waveform.

* 如果您需要申请我司样品,请填写表格提交,我们会24小时内回复您