在PMOS断开的时候,输出电压Vout出现回沟现象

电路现象:PMOS断开后,输出端Vout电压先降低,后上升,再下降,随即下电波形出现回沟。(由以下电路展开)

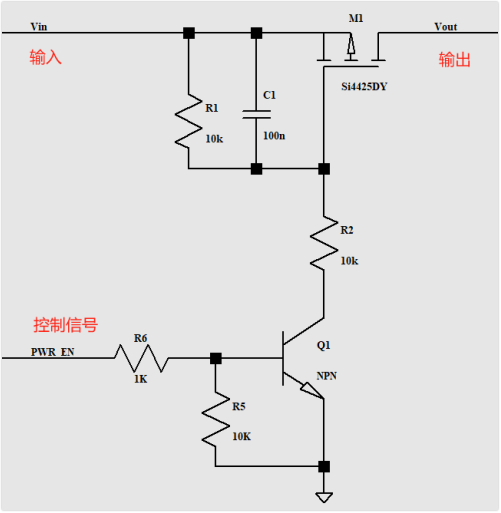

![1714361927414977.jpg 810a19d8bc3eb135e5ef197e370e04defc1f44ed[1].jpg](/data/upload/image/20240429/1714361927414977.jpg)

以上为PMOS开关仿真电路,其将负载换成了一个开关电路,在改变负载以后,Vout的下电波形就不正常了,这是为什么呢?

PMOS从导通到关断时,PMOS的阻抗会从接近0(导通),再到电阻无穷大(断开),这里会有一段过程,而PMOS会存在一定的阻值,负载也非恒定电阻。

在Vout下电过程中,负载获得的电压会下降到一定程度,随后可能会因为欠压突然停止工作,所需要的电流会急剧减小。

即其等效电阻突然变大,导致它获得的分压变大,这时就会出现以上的情况,Vout电压就涨上去了。也就是说,Vout的电压等于Vin在PMOS和负载上面的分压,如果负载RL突然变大,那么就有可能出现Vout突然上涨的情况。

![1714361934372241.jpg aa18972bd40735fa6710589f0c41a3be0e2408d5[1].jpg](/data/upload/image/20240429/1714361934372241.jpg)

因此,当PMOS从导通到关断切换期间,PMOS的Vgs电压等于其Vgsth,就出现了回沟。

![1714361941190641.png aa64034f78f0f73629754a3f98451f14ebc41326[1].png](/data/upload/image/20240429/1714361941190641.png)

那要如何解决这个问题呢?有两个选择。

1、可以让PMOS更快的关闭,例如将PMOS的g和s跨接的电容从100nF调整到10nF,回沟就基本没有了。

![1714361946226876.jpg bd315c6034a85edfdf87c73dda44a52edd547546[1].jpg](/data/upload/image/20240429/1714361946226876.jpg)

2.在输出端加一个滤波电容,避免负载等效RL突然变大。

这是因为增加一个滤波电容以后,等效负载会变成原本的RL和新增加电容阻抗的并联。尽管原本的RL突然变大,由于有电容阻抗的存在,负载阻抗就不会超过电容的阻抗。

PMOS关断的瞬间,过程是比较短暂的,信号可以当作交流,因此电容在这不可以看成是 开路,而是构成总的阻抗的一部分。

只要电容值合理,基本是可以解决电容回沟问题的。(如下图)

![1714361952578487.png 95eef01f3a292df55f0e035b2e21f06d35a87349[1].png](/data/upload/image/20240429/1714361952578487.png)

![1714361958599162.png aec379310a55b31943b4a236d1b92e2bcefc17c5[1].png](/data/upload/image/20240429/1714361958599162.png)

![1714361968594360.png a1ec08fa513d269726d7483ec7eb1ef64316d86f[1].png](/data/upload/image/20240429/1714361968594360.png)

![1714361974948185.png 11385343fbf2b211336736a05890c9350dd78eb5[1].png](/data/upload/image/20240429/1714361974948185.png)

* 如果您需要申请我司样品,请填写表格提交,我们会24小时内回复您