本文介绍了五种MOS管在实际应用中存在的漏电流:反偏结泄漏电流、栅极致漏极泄漏电流、栅极直接隧穿电流、亚阈值泄漏电流和隧穿栅极氧化层漏电流。这些漏电流会影响低功耗设备电池的寿命和s&h电路信号保持时间。为了减小漏电流,可以使用高K介电材料替代SiO2作为栅极绝缘体介质层。同时,亚阈值泄漏电流在CMOS技术中较大,可以通过降低阈值电压来减小其影响。

本文介绍了五种MOS管在实际应用中存在的漏电流:反偏结泄漏电流、栅极致漏极泄漏电流、栅极直接隧穿电流、亚阈值泄漏电流和隧穿栅极氧化层漏电流。这些漏电流会影响低功耗设备电池的寿命和s&h电路信号保持时间。为了减小漏电流,可以使用高K介电材料替代SiO2作为栅极绝缘体介质层。同时,亚阈值泄漏电流在CMOS技术中较大,可以通过降低阈值电压来减小其影响。

摘要由作者通过智能技术生成

有用

有用

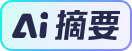

在实际应用中,MOS管常常存在各种漏电流,这使得它严重减少了低功耗设备电池的使用寿命,以及在一些s&h电路中,限制了信号保持时间。而一个理想的MOS管是不应该存在任何电流流入衬底的,特别是当MOS管关断时,漏-源极之间不应该存在任何电流。

那么,今天我们来了解MOS管以下5种漏电流。

反偏结泄漏电流

:当MOS管关断时,通过反偏二极管从源货漏极到衬底。

其主要由两部分组成:

1. 由耗尽区边缘的扩散和漂移电流产生

2. 由耗尽区中的产生的电子-空穴对形成

在一些重掺杂的PN区,还会携带一些间隧穿(BTBT)现象贡献的泄漏电流。不过源漏二极管和阱二极管的结反向偏置泄露电流分量,相对于其他三个泄漏分量几乎可以忽略不计。

栅极致漏极泄漏电流

栅极致漏极泄漏电流一般由MOS管漏极结中的高场效应引起的。由于源极和漏极重叠区域之间存在大电场而发生隧穿(包含雪崩隧穿和BTBT隧穿),产生了 电子-空穴对。由于电子被扫入阱中,空穴积累在楼中形成/GIDL。

栅极与漏极重叠区域下的强电场,会导致深度耗尽区,以及使漏极和阱交界处耗尽层变薄,因而有效形成漏极到阱的电流/GIDL。/GIDL与VGD有关,一般NMOS的/GIDL会比PMOS的大两个数量级。

栅极直接隧穿电流

栅极泄漏电流是由栅极上的电荷隧穿过栅氧化层进入阱(衬底)中形成。一般栅氧化层厚度在3-4nm,由于在栅氧化物层上施加高电场,电子通过Fowler-Nordheim隧道进入氧化物层的导带而产生的/G。

随着晶体管长度和电源电压的减小,栅极氧化物的厚度也必须减小,以维持对沟道区域的有效栅极控制。不幸的是,由于电子的直接隧穿会导致栅极泄漏呈指数级增加。

目前可以使用高K介电材料(如TiO2和Ta2O5),替代SiO2作为栅极绝缘体介质层。

这种方法可以克服栅极漏电流,并同时对其栅极保持良好的控制。

亚阈值泄漏电流

:指沟道处于弱反型状态下的源漏电流,是由器件沟道少数载流子的扩散电流引起的。当栅源电压低于阈值电压Vth时,器件不会马上关闭,而是进入了“亚阈值区”而IDS成了VGS的指数函数。

在目前的CMOS技术中,亚阈值泄漏电流ISUB会比其他泄漏电流分量大得多。这主要是因为现代CMOS器件中的VT相对较低。

隧穿栅极氧化层漏电流

在短沟道器件中,薄栅极氧化物会在 SiO2 层上产生高电场。由于高电场作用,低氧化物厚度会导致电子从衬底隧穿到栅极,同时从栅极通过栅极氧化物,隧穿到衬底,进而形成栅极氧化物的隧穿电流。

![1714360430543986.jpg cb8065380cd791232f6b60d1db0d228fb3b78057[1].jpg](/data/upload/image/20240429/1714360430543986.jpg)

(a)是一个平带 MOS 晶体管,即其中不存在电荷。

当栅极端子正偏置时,能带图会发生变化,如图(b)。强烈反转表面处的电子隧道进入或穿过 SiO 2层,从而产生栅极电流。

另一方面,当施加负栅极电压时,来自 n+ 多晶硅栅极的电子隧道进入或穿过 SiO 2层,从而产生栅极电流,如图 (c) 所示。

![1714360435526053.png bba1cd11728b471097ec611bb6f7b8f0fe0323e8[1].png](/data/upload/image/20240429/1714360435526053.png)

![1714360442198986.png 72f082025aafa40f8569d6eed05d784278f01918[1].png](/data/upload/image/20240429/1714360442198986.png)

* 如果您需要申请我司样品,请填写表格提交,我们会24小时内回复您