本文要点:

1. 寄生电容的定义

2. 电路中寄生电容的来源

3. 测量和分析寄生电容的方法

4. 如何减少寄生电容的影响

一、定义

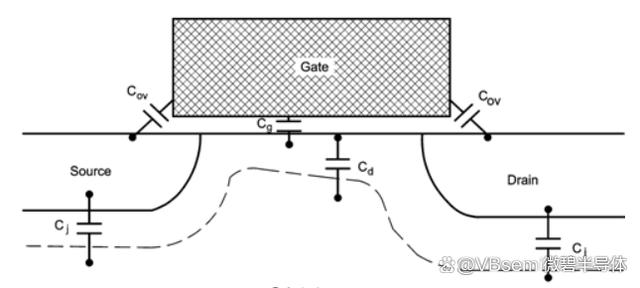

寄生电容是一种现象,即电路中的元件在物理上不是电容时表现得像电容。

含义:原本没有在那个地方设计电容,但由于布线之间总是有互容,互容就好像是寄生在布线之间的一样,所以叫寄生电容,又称杂散电容。(官方解释)

寄生电容本身不是电容,根据电容的原理:电容一般由两个极板和绝缘介质构成。因此寄生电容无法避免的。

![1714297397926337.png aa64034f78f0f736e25b7b97ab32b414eac41376[1].png](/data/upload/image/20240428/1714297397926337.png)

(导体间寄生电容是面积与距离的关系)

由此我们能够得知,它是由于电子元器件的结构、材料等因素导致的,因此寄生电容无法避免的。同时,寄生电容的存在会对电路的性能产生影响。

二、电路中的寄生电容

寄生电容在电路中时常出现,一般来源于以下几个方面:

a. 元件之间的电容(不同元件之间的导线、引脚等产生的)

b. 元件与地之间的电容(元件与地之间的导线、引脚等产生)

c. PCB板上的电容(不同导线之间、导线与地之间形成)

d. 其他因素(电磁干扰、温度变化等产生)

在电路中,寄生电容会导致信号的衰减和相位移动,从而影响其的性能和稳定性。

特别是在高频电路中更为明显,在高频电路中,寄生电容会导致信号的失真和噪声的增加。

三、测量和分析寄生电容的方法主要有:

- 使用LCR表进行测量;

- 使用示波器和信号发生器进行测量;

- 使用频率响应分析器

(以上方法都存在一定的误差风险,实际应用需要进行校准和误差分析。)

四、如何减少寄生电容

为此我们需要采取一些措施来减小寄生电容的影响:

1. 尽可能缩短元件之间的距离,从而减小元件之间的电容。

2. 将元件引脚与地之间的距离尽量缩短,减小元件与地之间的电容。

3. 合适的PCB布局,有效减小PCB板上的电容。

4. 采用屏蔽措施,以便减小电磁干扰。

此外,我们还可以利用补偿电路,例如使用电容器和电感器来抵消寄生电容的影响,还可以使用高速缓存和其他优化技术来提高系统的性能和稳定性。

(寄生电容)

* 如果您需要申请我司样品,请填写表格提交,我们会24小时内回复您