When the PMOS is turned off, an undershoot phenomenon occurs in the output voltage Vout.

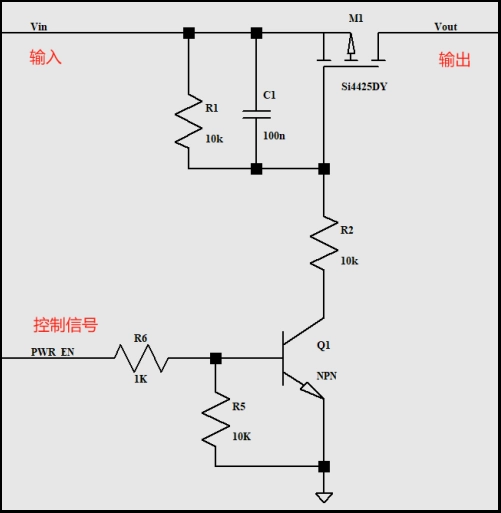

Circuit Phenomenon: After the PMOS is turned off, the output voltage Vout first decreases, then increases, then decreases again, resulting in an undershoot waveform during power down. (As illustrated in the circuit below)

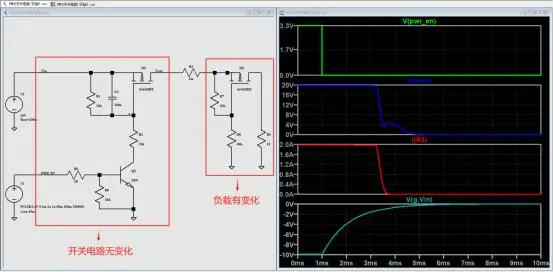

The above is a simulation circuit of a PMOS switch, where the load is replaced with a switching circuit. After changing the load, the power-down waveform of Vout becomes abnormal. Why is this?

When the PMOS transitions from conducting to non-conducting, its impedance changes from nearly 0 (conducting) to infinite (non-conducting). There is a transitional period where the PMOS exhibits some resistance, and the load may not have a constant resistance.

During the power-down process of Vout, the voltage obtained by the load may decrease to a certain extent and then abruptly stop working due to undervoltage, causing the required current to sharply decrease. This sudden increase in the effective resistance of the load results in a larger voltage drop across it, causing the Vout voltage to rise. Essentially, Vout voltage equals the voltage division of Vin across the PMOS and the load. If the load RL suddenly increases, Vout may unexpectedly rise.

Therefore, during the transition from conducting to non-conducting of the PMOS, when the PMOS's Vgs voltage equals its Vgsth, undershoot occurs.

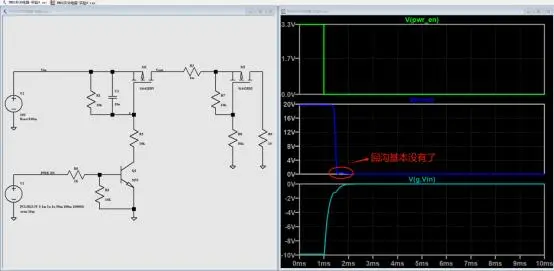

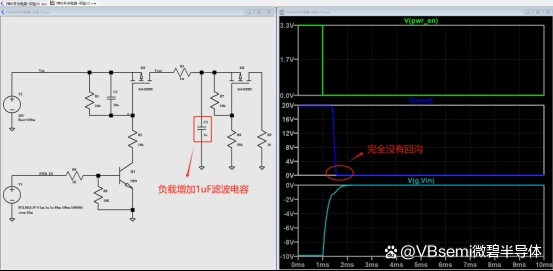

So, how can this problem be addressed? There are two options:

PMOS can be made to turn off faster, for instance, by reducing the capacitance across PMOS's gate and source from 100nF to 10nF, which reduces undershoot substantially.

Adding a filter capacitor at the output terminal can prevent the equivalent load resistance RL from suddenly increasing.

Adding a filter capacitor makes the equivalent load consist of the original RL and the added impedance of the capacitor in parallel. Even if the original RL suddenly increases, due to the presence of capacitor impedance, the load impedance will not exceed the impedance of the capacitor.

During the moment when the PMOS is turned off, the process is relatively short-lived, and the signal can be treated as alternating current. Therefore, the capacitor in this scenario cannot be considered an open circuit but rather forms a part of the total impedance.

As long as the capacitor value is reasonable, it can effectively address the issue of undershoot caused by the capacitor.

* 如果您需要申请我司样品,请填写表格提交,我们会24小时内回复您