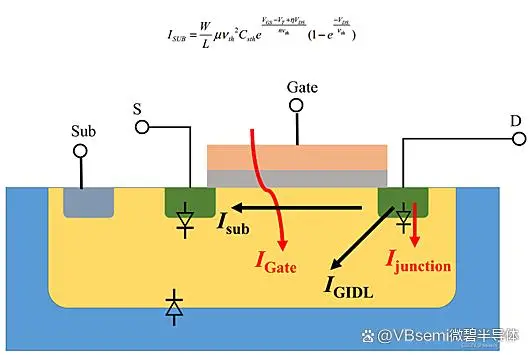

In practical applications, MOSFETs often exhibit various leakage currents, which seriously reduce the battery life of low-power devices and limit the signal retention time in some s&h circuits. An ideal MOSFET should not have any current flowing into the substrate, especially when the MOSFET is turned off, and there should be no current between the drain and source when the MOSFET is in the off state.

So today, let's learn about the following 5 types of leakage currents in MOSFETs.

Reverse Bias Junction Leakage Current:

When the MOSFET is turned off, there is a reverse bias diode from the source or drain to the substrate.

It mainly consists of two parts:

Generated by diffusion and drift currents at the edge of the depletion region

Generated by electron-hole pairs formed in the depletion region

In some heavily doped PN regions, there will also be a contribution to the leakage current from the phenomena of band-to-band tunneling (BTBT). However, the leakage current component of the source-drain diode and the well diode biased in reverse direction can be almost negligible compared to the other three leakage components.

Gate-to-Drain Leakage Current:

Gate-to-drain leakage current is generally caused by the high field effect in the MOSFET's drain junction. Due to the large electric field between the source and drain overlap region, tunneling occurs (including avalanche tunneling and BTBT tunneling), generating electron-hole pairs. Since electrons are swept into the well, holes accumulate in the channel forming GIDL.

The strong electric field below the gate overlap region causes a deep depletion region and thins the depletion layer at the junction of the drain and well, thereby effectively forming a current/GIDL from the drain to the well. /GIDL is related to VGD, and generally, the /GIDL of NMOS is two orders of magnitude larger than that of PMOS.

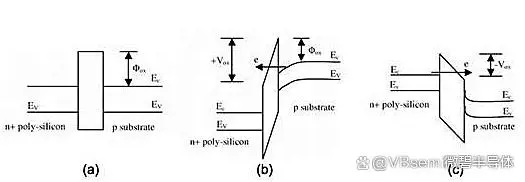

Gate Direct Tunneling Current:

Gate leakage current is formed by charge tunneling through the gate oxide layer into the well (substrate). Generally, the gate oxide layer thickness is 3-4nm. Due to the application of a high electric field on the gate oxide layer, electrons tunnel through the Fowler-Nordheim tunnel into the conduction band of the oxide layer, forming /G.

As the transistor length and power supply voltage decrease, the thickness of the gate oxide layer must also decrease to maintain effective gate control over the channel region. Unfortunately, direct tunneling of electrons leads to an exponential increase in gate leakage.

Currently, high-K dielectric materials (such as TiO2 and Ta2O5) can be used to replace SiO2 as the gate insulation layer.

This method can overcome gate leakage current while maintaining good control of the gate.

Subthreshold Leakage Current:

Refers to the source-drain current when the channel is in a weakly inverted state, caused by the diffusion current of minority carriers in the device channel. When the gate-source voltage is lower than the threshold voltage Vth, the device does not immediately turn off but enters the "subthreshold region," and IDS becomes an exponential function of VGS.

In current CMOS technology, the subthreshold leakage current ISUB is much larger than other leakage current components. This is mainly because the VT in modern CMOS devices is relatively low.

Gate Oxide Layer Tunneling Leakage Current:

In short-channel devices, a thin gate oxide layer will produce a high electric field on the SiO2 layer. Due to the high electric field, the thin oxide thickness causes electrons to tunnel from the substrate to the gate, then through the gate oxide, tunneling back to the substrate, thereby forming gate oxide tunneling current.

(a) depicts a flat-band MOS transistor, where there is no charge.

When the gate terminal is positively biased, the energy band diagram changes, as shown in (b). Electrons strongly tunnel through or penetrate the SiO2 layer at the inverted surface, generating gate current.

On the other hand, when a negative gate voltage is applied, electrons from the n+ polycrystalline silicon gate tunnel through or penetrate the SiO2 layer, generating gate current, as shown in (c).

* 如果您需要申请我司样品,请填写表格提交,我们会24小时内回复您