Actual power applications commonly include DCDC and LDO, with the main difference being that the operating state of the LDO output transistor is linear, not switching mode.

Today, we will mainly focus on explaining the application principles of NMOS and PMOS in LDO, and delve deeper into the DCDC section later.

Working Principles of LDO

Transistors operating in the linear region can be treated as voltage-controlled current sources, used to control the circuit and continuously monitor the output voltage. Then, based on the load requirements, the current source is adjusted to ensure that the output voltage remains at the desired value.

The design limit of the current source comes into play: it limits the maximum load current that the regulator can supply while maintaining voltage regulation.

NMOS Type LDO

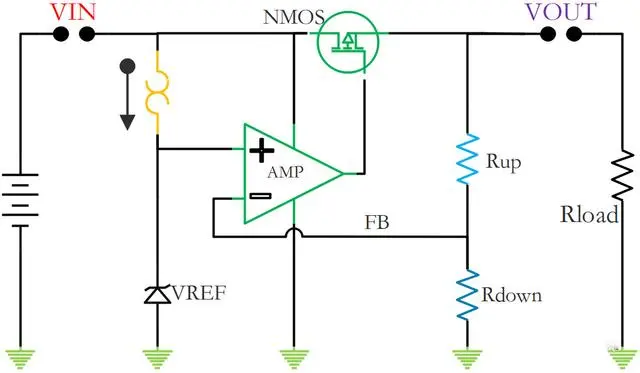

Let's take a look at the diagram below:

[Diagram showing NMOS Type LDO]

In this circuit, the limitation on the voltage difference between the input and output is determined by the minimum voltage difference between the gate and drain of the MOS transistor.

The NMOS Type LDO uses a pair of resistors to sample the output voltage and sends it to the input of the error amplifier, where it is compared with a reference voltage. The voltage is then amplified in the error amplifier, ultimately generating a voltage signal to control the gate of the NMOS transistor.

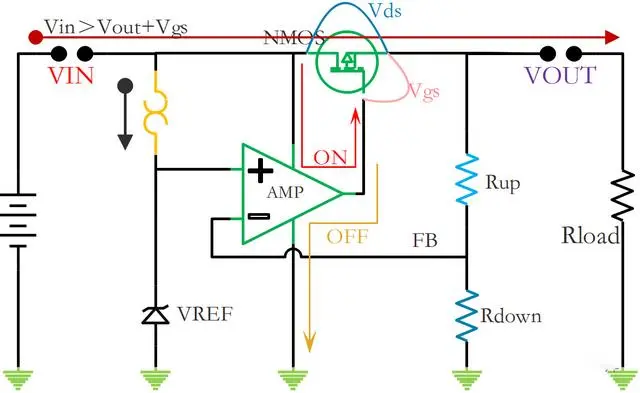

[Diagram depicting the direction of load current in NMOS]

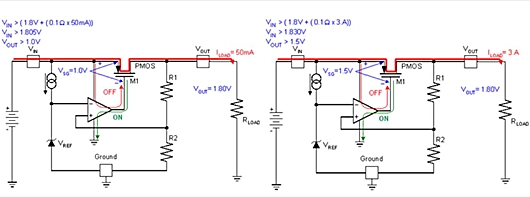

At load currents of 50mA and 3A, the static current required by the NMOS Type LDO is almost the same. Despite the significant variation in load, the static current hardly changes.

This is because NMOS only requires voltage signal control, and the voltage signal does not need to be consumed by the current of the error amplifier itself.

Therefore, static current becomes the biggest advantage of NMOS Type LDO.

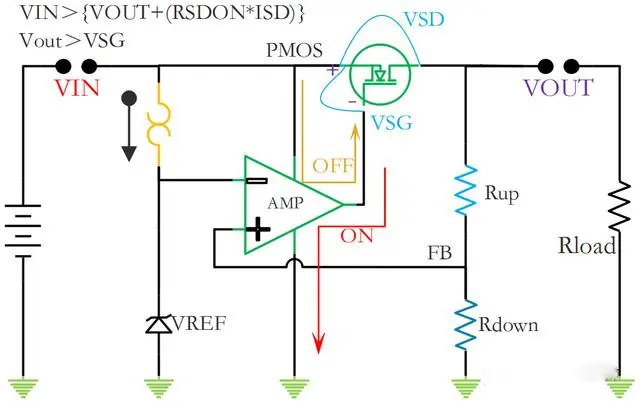

PMOS LDO

Compared to NMOS Type LDO, due to the conduction threshold between the source and gate of NMOS, the voltage difference between the input and output must be greater than this conduction threshold, which is significant. At this point, we can use PMOS Type LDO to reduce this part of the enablement.

In PMOS, we need the gate voltage to be lower than the source voltage to allow PMOS to conduct, and this voltage difference must be greater than the conduction threshold of PMOS to ensure that the error amplifier can pull the gate of PMOS to the appropriate voltage range throughout the range.

Since the main power part uses PMOS transistors, also controlled by voltage, the variation in load current results in hardly any change in the static current of the error amplifier.

Here we can see that NMOS, due to the conduction threshold between the source and gate, imposes limitations on the input-output voltage difference. PMOS Type LDO driving is much simpler compared to it.

Summary:

NMOS Type LDO can provide fast transient response but requires two bias power supplies for device operation.

PMOS Type LDO can achieve voltage drop and can operate under a single power supply. However, it is limited by the VGS characteristics of the transfer transistor at low input voltages. At the same time, they do not have many of the protection features provided by high-performance LDOs.

Common LDOs are generally composed of P-type transistors, but their efficiency is relatively low, so they are generally not used in high-current applications. In some scenarios with high current and low voltage drop, N-type LDOs may be used.

* 如果您需要申请我司样品,请填写表格提交,我们会24小时内回复您