Previously, VBsemi shared a video discussing a circuit design for automatic switching between two power sources, utilizing three MOSFETs. Recently, two other practical circuit designs for main and auxiliary power automatic switching caught our attention, and we'd like to share them with you.

Circuit Design with PMOS and Diode

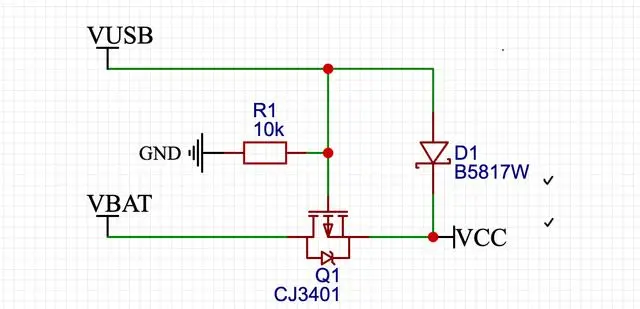

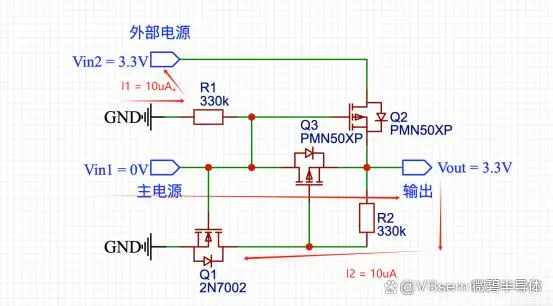

We'll focus on the following circuit diagram:

VUSB: External USB power supply

VBAT: Lithium battery power supply

Q1: PMOS

D1: Diode

Circuit Operation:

When the external power supply is connected, the lithium battery supply is disconnected.

When the external power supply is disconnected, power is supplied by the lithium battery.

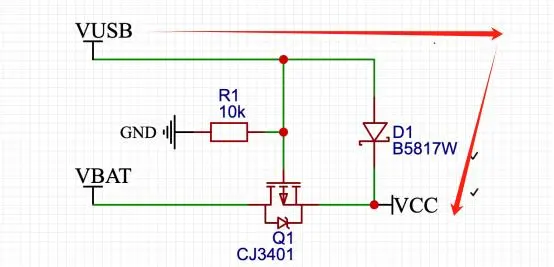

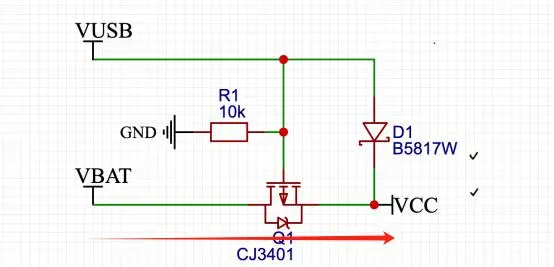

When VUSB supplies power (5V), the voltage at the gate (G) of the PMOS is 5V, so the PMOS does not conduct. The voltage then passes through diode D1 directly to VCC.

When VUSB is disconnected, the voltage at the gate (G) of the PMOS (5V) is pulled down to GND through resistor R1. In this case, the PMOS conducts, and VCC is powered by VBAT (the lithium battery).

It's worth noting that before the MOSFET conducts, the voltage at the source (S) is higher than at the gate (G), causing the MOSFET to conduct. Once the MOSFET conducts, its parasitic diode shorts, and no longer functions.

Achieving Zero Voltage Drop for Main and Auxiliary Power Automatic Switching

In the previous circuit, adding diode D1 made achieving zero voltage drop difficult, as D1 has a minimum voltage drop of 0.3V.

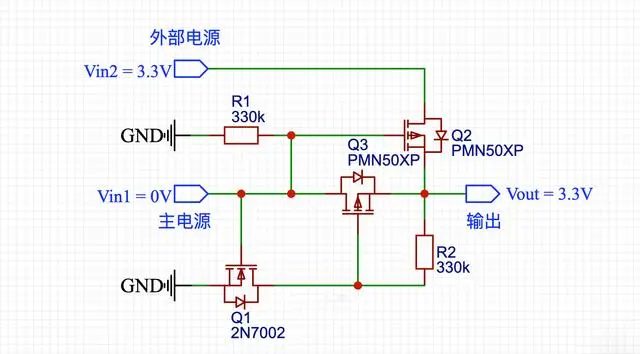

Consider the following circuit, which utilizes the low on-resistance (RDS(on)) characteristic of MOSFETs to improve efficiency:

This circuit uses 3 MOSFETs in the design:

When VIN1 (main power supply) is 3.3V, Q1's NMOS conducts, pulling down the gate of Q3 PMOS, causing Q3 to conduct.

At this point, the voltage between the gate and source of Q2 MOSFET is approximately equal to the on-resistance of Q3 PMOS, which is about tens of mV. Therefore, Q2 MOSFET turns off, disconnecting VIN2 (external power supply), and VOUT is powered by VIN1, resulting in VOUT = 3.3V.

The static power consumption of the circuit at this point is I1 + I2 = 20uA.

When VIN1 (main power supply) is disconnected, Q1 NMOS turns off. The gate of Q2 PMOS is pulled down by R1, causing Q2 to conduct. The gate of Q3 PMOS is pulled up by R2, causing Q3 to turn off.

At this point, both Q1 and Q3 are off, and VOUT is powered by VIN2, also at 3.3V.

The static power consumption of the circuit is still I1 + I2 = 20uA.

In this circuit, when the circuit is powered by VIN2 (external power supply), the static power consumption "disappears" and becomes zero. The circuit virtually has no voltage drop, unless the current is very large.

It can be concluded that in this circuit, powering the circuit with the external power supply is the better choice.

One condition is that all three MOSFETs in the circuit should have low on-resistance and low voltage characteristics.

However, some users have reported that in the process of the main power supply decreasing, there may be some issues: Q3 is not completely turned off before Q2 starts to conduct, creating a path for the external power supply through Q2 and Q3, preventing the main power supply from decreasing.

Specific situations need to be observed in actual applications. If you have better suggestions or questions, feel free to leave a comment in the comment section!

That's all for this issue. Your attention and support are my motivation for continuous creation! Thank you for your support!

* 如果您需要申请我司样品,请填写表格提交,我们会24小时内回复您