In power supply applications, PMOS is often used as a switch. When the load has a large capacitive load, the PMOS will cause a drop in the front-end power supply voltage when it is turned on. Why is this happening?

The drop in the front-end power supply voltage at the moment of turn-on is because the switch speed is too fast, causing a charging current when the MOS tube is turned on. The key to solving this problem is to reduce the charging speed of the large-capacity capacitor.

For example, in some circuits, there are many circuits in simultaneous use in the secondary power supply. In this case, many filtering capacitors are connected, resulting in a large total capacitance. When the power is suddenly turned on, these capacitors need to be charged, which is a large capacitance.

Because a large current is needed at the beginning, the front-end is unable to provide it in time, ultimately causing the power supply to be pulled down.

So, how can we reduce the capacitance of the large capacitor to avoid this situation?

We mainly focus on three measures (but not limited to):

Series resistance

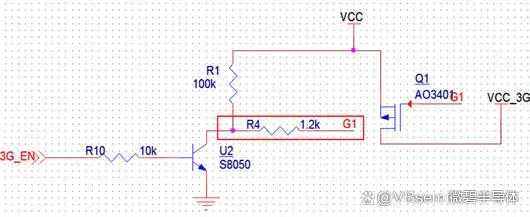

Series resistors can be placed between PMOS and the capacitor, above the capacitor, or before PMOS. Essentially, this can reduce the charging current of the front-end power supply to the capacitor.

For series resistors, we have mentioned many times before that they can reduce the charging speed of the capacitor and reduce the corresponding load capacity. However, when serial resistors are placed before PMOS, attention should be paid to the size of the serial resistor, which needs to be determined by the average value of the maximum load current and the maximum current of PMOS.

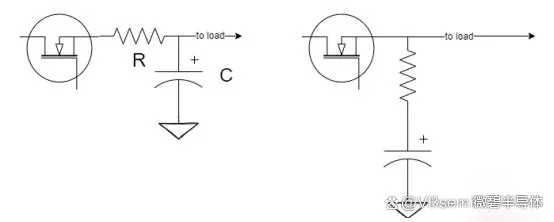

Increase power supply capacitance

Capacitors can be connected in parallel between the gate and source of PMOS, or between the gate and drain. This can reduce the turn-on speed of PMOS by indirectly controlling the charging current of the capacitor through controlling the channel width of PMOS.

In addition, you can also choose to increase a capacitor of appropriate size at the input of the front-end power supply to buffer and suppress the fluctuation of the power supply, reducing the amplitude of the power supply drop.

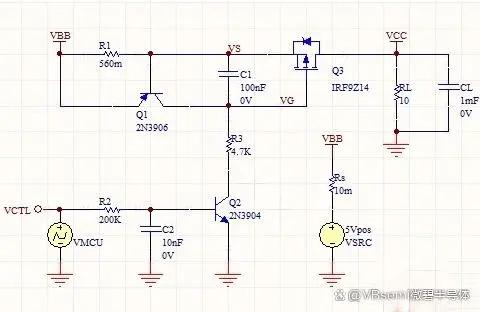

Increase power supply voltage regulator or follower

In the face of a sudden increase in load, the regulator can ensure the stability of the output voltage, while the follower can automatically adjust the output voltage through negative feedback.

Well, that's about it for this issue. Follow me, and we'll see you in the next issue!

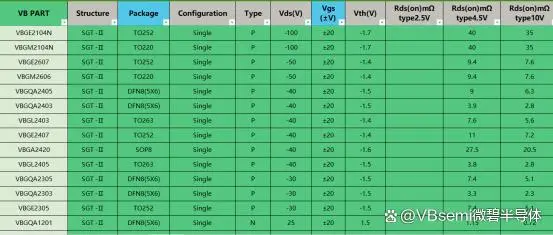

* 如果您需要申请我司样品,请填写表格提交,我们会24小时内回复您