In electronic applications, using two PMOS transistors connected back-to-back is a common circuit design, primarily aimed at improving the stability and reliability of the circuit.

So, when two PMOS transistors are connected back-to-back, are they in series or parallel? In fact, they are both, meaning there are both series and parallel connections. Today, we will mainly focus on the following two points:

The purpose of series and parallel circuit design

Why can't we just use one PMOS?

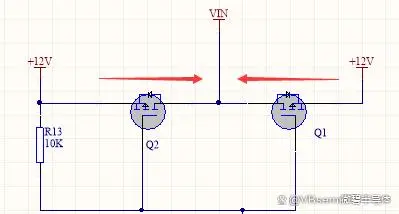

Two PMOS transistors in parallel, as shown in the diagram

It can be seen that when Q1 and Q2 (PMOS) are conducting, the +12V on both sides is connected in parallel to increase the current. This is done to increase the load capacity of VIN (output) for powering the module.

The usefulness of these two PMOS transistors is clear here: they act as a shunt because the VIN load current can be quite high.

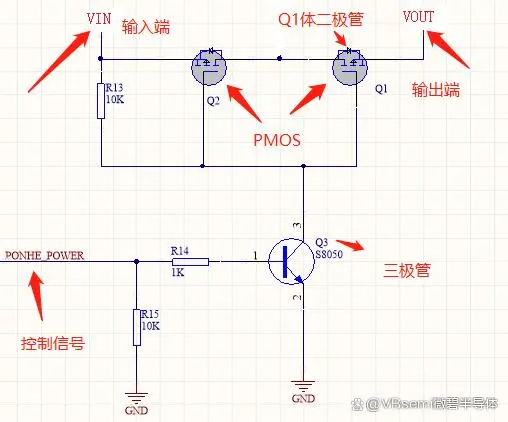

Explanation of the circuit design here:

Control signal, which is PHONE_POWER;

When it outputs a high level, the transistor Q3 conducts, and both PMOS Q1 and Q2 conduct, making the VIN output equal to +12V; when it outputs a low level, the transistor Q3 cuts off, and both PMOS Q1 and Q2 cut off, making the VIN output equal to 0V;

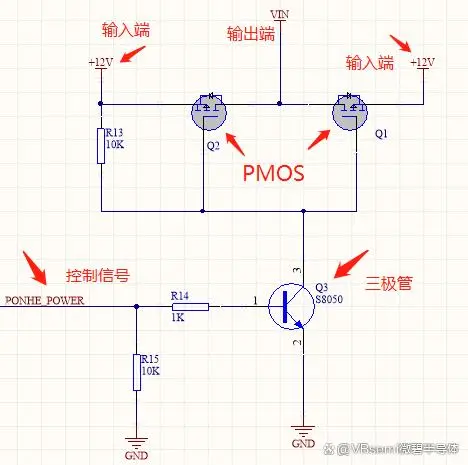

Two PMOS transistors in series, as shown in the diagram

It can be seen that the two MOS transistors are connected in series. Explanation of the circuit design:

Control signal, which is PHONE_POWER;

When it outputs a high level, the transistor Q3 conducts, and both PMOS Q1 and Q2 conduct, making the VIN input equal to the VOUT output; when it outputs a low level, the transistor Q3 cuts off, and both PMOS Q1 and Q2 cut off, making the VIN output equal to 0V;

When an external output terminal VOUT needs to be debugged, the two PMOS transistors are turned off to prevent the output current of VOUT from flowing to the VIN input. If there is no Q1, the output current of VOUT will flow to the VIN input through the body diode of Q2.

The principle is based on the reverse cutoff characteristic of the body diode: Q1 (positive on the left and negative on the right), Q2 (negative on the left and positive on the right).

So, why can't we just use one MOS transistor?

Now let's discuss the circuit design:

Assuming the maximum load current of VIN is 1A, using two PMOS transistors in parallel in the circuit, the current passing through each PMOS transistor will be 0.5A or more.

But the question is, can we guarantee that both transistors carry exactly 0.5A? If one carries 0.7A and the other carries 0.3A, or one carries 0.6A and the other carries 0.4A, then one transistor will overheat due to the excessive current and may even burn out?

The first thing that comes to mind is to use two MOS transistors with the same RDS(on) value, so that the current flowing through them will be the same.

But as the saying goes, there are no two leaves exactly alike in this world. MOS transistors are the same, and there will be differences in manufacturing processes and other parameters between two transistors of the same type.

At this point, did anyone think of an article we published before? It's about the current sharing design of MOS transistors.

It's still related to the RDS(on) of MOS transistors. I saw some friends saying that.

The RDS(on) of MOS transistors is positively correlated with temperature, that is, as the temperature rises, RDS(on) increases.

Since the current flowing through Q1 will be greater than that of Q2, the temperature rise of Q1 will definitely be higher than that of Q2. At this time, the RDS(on) of Q1 will increase. After the RDS(on) increases, the current flowing through Q1 will decrease, forming a complete negative feedback loop and achieving current sharing.

However, to be on the safe side, it is recommended to choose a MOS transistor with a margin when selecting MOS transistors. For example, if the maximum load of VIN is 1A, then two PMOS transistors can be selected with IDS of 0.6~0.7A. It is also best to choose the same model.

The advantages of this circuit design, summed up by Micro Crystal, are as follows:

Current sharing to avoid the risk of damaging devices due to excessive current;

Increase the switching speed, as two transistors in parallel can reduce the switching time of the entire circuit. The lower the resistance, the faster the switching speed;

Reduce electromagnetic interference, as back-to-back connection can reduce the electromagnetic interference generated during switching;

Improve circuit reliability. When one PMOS transistor fails, the other PMOS transistor can still continue to work;

Cost reduction. Choosing MOS transistors can reduce the total cost to some extent.

The related advantages and application analysis will be discussed later when we have the opportunity!

Can you please like or follow if you've read this far? Your support is greatly appreciated! If you have any questions or topics you'd like to discuss, feel free to comment and exchange ideas!

* 如果您需要申请我司样品,请填写表格提交,我们会24小时内回复您